如何计划DDR路由的PCB布局

关键的外卖

设置您的设计规则,约束,足迹,通过DDR路由。

考虑路由DDR内存。

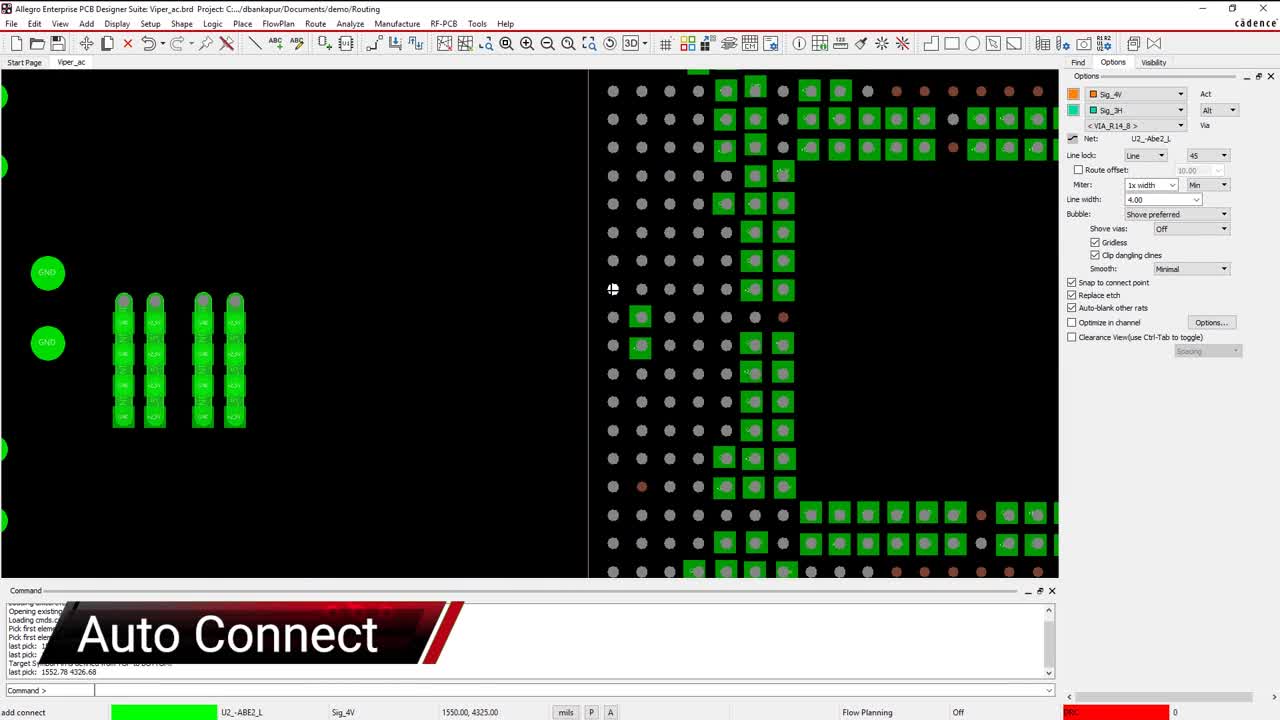

你的PCB设计工具可以帮助你和DDR内存路由。

DDR4内存模块

现在20多年,DDR内存PCB设计不可分割的一部分。最初的DDR内存很快取代DDR2,然后DDR3,最后由DDR4。然而,随着每一个新的迭代的DDR内存的PCB设计挑战变得更加复杂。销数量增加和设计约束变得紧缩,导致很多网需要完全由PCB设计路由。

成功的关键在路由DDR内存是你开始前要做好充分的准备。这意味着计划你的PCB设计从一开始的路由,你需要做的。板材料,层分层盘旋飞行,组件位置,通过类型和路由拓扑都是提前计划。这里有一些更多的细节如何在你的下一个计划DDR路由PCB设计。

设置您的设计成功的DDR内存路由

第一步准备设计一个董事会DDR内存路由计划董事会层和配置。因为你将处理高速电路,您可能需要考虑其他比标准FR-4板材料。但最重要的部分将配置设计层董事会。尽管你可以挤压致密路由到较少的层,这将最有可能不是最好的配置信号的完整性。你可能看12层的分层盘旋飞行DDR路由由于密度较高的设备,和带状线和双带状线层配置的必要性。

下一步将在建立的规则和高速约束设计。很多规则应该已经包含在数据的设计示意图。你很可能会发现更多的规则需要加载到数据库布局,虽然。这就是工作与设计团队的所有成员将偿还你收集和组织的规则和约束的设计。因为很多你的设计可能拥有相似的特征和特性,往往是有用的保持图书馆的设计规则和约束从以前的设计。这将帮助你减少的时间花在这项任务上。

对于任何设计,你要花大量的时间确保PCB组件的足迹和土地模式是正确的在你开始。这将节省你很多时间后必须正确和更新部分不正确的放在第一位。这样的错误不仅会削弱你的日程表,但它可能涉及大量的返工如果一个更新的部分不再适合位置和路由,你已经完成。

您还必须创建新的脚印你从未用过的设备,如DDR内存部分。这就是你的在线图书馆资源可以是一个很大的帮助,比如统一部分搜索功能在节奏快速的PCB设计工具。符号与PCB图书馆工作的更多信息,看一下规则原理图符号在这个电子书。

建立微分对快板的约束管理器

如何计划DDR路由使用最好的位置和通过逃

良好的DDR路由计划要求你首先有良好的组件的位置。你们之前用过的高速设计方法仍然是重要的在这里:

信号路径:在高速设计,您需要考虑整个信号路径敏感的电路,而不是只考虑的点对点连接。这意味着在顺序示意图将部分工作保持整个路径从司机到接收器,和之间的任何部分,尽可能接近。

内存设备:这些部件需要被放置接近最小化他们,让他们分组之间的路由。他们也应该放置在秩序,从最高的最低数据位和结束。

路由通道:会有很多网路线和DDR内存需要故意把你的部分预期的路由你需要的房间。这样做将包括足够的空间通过逃避模式。

敏感电路:让你敏感的高速电路有足够的空间隔离干扰。噪音可以来自其它信号如时钟,或电源电路。

旁路电容:保持信号完整性的记忆回路,你会把更多的绕过帽稳定的参考电压。一定要给自己足够的空间为这些帽子,不吃这个房间已经预留给路由和逃避通过。

你可以找到更多细节将组件通过阅读这本书成功的步骤设置和位置从节奏。说到逃避通过,成功路线DDR内存,您将需要有一个好的通过式擒纵机构计划在你的布局。

首先,你将不得不决定使用哪个通过;通孔、盲或埋葬。你甚至可能想使用微通过给自己更多的空间,但要意识到这样做的成本增加。你很多通过逃将从高引线数球栅阵列(BGA)部分。脚距越小,越需要使用通过BGA垫。这将帮助你与路由BGA的模式,却又有一种权衡与制造业的复杂性和成本。一个很好的资源就是检查供应商的DDR组件来找出他们的建议通过逃避路由模式。

高速路由与调谐痕迹

DDR内存路由方面的考虑

现在,您可以开始计划你的可用不同的路由策略DDR内存路由。你的路由拓扑将取决于你的信号处理。菊花链路由用于地址和控制路由,而使用点对点的路由等敏感电路微分对。DDR路由,然而,有一些具体的拓扑需要注意的:

T-Topology:这是用于老DDR路由是无法处理,介绍了信号率较高的DDR3 DDR4。T-Topology将路线时钟、命令和地址信号分支的方式从控制器到内存设备而直接连接数据行。

Fly-by-termination:飞行路由与T-topology的不同之处在于,它将时钟,路由命令和地址在一个链从控制器到不同的存储设备。数据行仍在DDR2直接连接一样。

抓斗:在这个配置中,内存设备是在前面和后面的板。这将导致更少的空间使用但复杂的路由。然而,如果成功了,这个策略可以帮助你路由设备之间通过共享通过顶部和底部的董事会。

拓扑你计划将取决于所需要的电路和董事会的布局。飞行拓扑在T-topologies相比有了很大改善,他们支持高频操作以及减少路由,使信号完整性和时机。进一步阅读等高速设计问题噪音和时机的问题,看看这个电子书从节奏。

因为一倍数据速率的DDR内存,它变得非常重要的准确路线你跟踪长度以满足设备的性能规格。能够发送和接收信号每个时钟周期的两倍,捕获的数据必须在时钟的上升和下降沿。要做到这一点,必须精确控制电路的时序,通过控制跟踪路由模式的长度。其他技巧PCB路由,看看这本书你的路线设计的成功。

设置最小/最大传播延迟净集团从内部约束管理器

你的工具可以帮助你进入下一个水平

有很多计划当你准备设计一个电路板和DDR路由。另一种方法,可以帮助自己做好准备这种级别的设计是使用内置先进的PCB设计工具路由特性和功能。您需要能够轻松地设置规则和设计约束正如我们上面提到的,和有多个特性来帮助你手动和自动路由是很重要的。当路由DDR内存,它也可以帮助区分不同的内存组颜色,你肯定会需要模拟和分析工具设计中内置的系统。

所有这些特性来帮助你与你的DDR路由可以找到最好的PCB设计系统。其中最先进的是快板PCB设计者从节奏。快板你不仅会有你所需要的完整的设计系统对于今天的DDR路由方面的考虑,但你也将准备好了下一个级别的DDR内存路由和超越。

如果你想了解更多关于节奏是如何对你的解决方案,跟我们和我们的专家团队。