BGA封装的顶级PCB布局建议

关键的外卖

更详细地检查BGA包。

探索BGA包的PCB布局建议。

学会利用PCB设计工具的强大功能来使用bga。

BGA足迹的3D布局,其下面是内部跟踪路由。

随着电子设备的性能不断增长,它们的尺寸也在不断缩小。为这些较小的设备提供必要的功能需要组件封装技术的最新进展。自20世纪80年代末引入以来,最受欢迎的组件包之一就是球栅阵列(BGA)。

在他们推出后不久,BGA包装作为包装技术的下一步开始登上头条。它们提供了比通孔PGA和表面贴装qfp更高的互连密度,且成本相当,而且没有与这些封装相关的制造问题。

他们的受欢迎程度从那里继续升级,他们已经成为默认的包用于高引脚数集成电路,如微处理器和存储设备。让我们更深入地研究这个问题,并讨论BGA包的一些PCB布局建议。

更详细地看球网格阵列包

球栅阵列封装封装复杂集成电路的模具,没有通孔或表面安装部件常见的引脚或引线。相反,他们有别针垫均匀地分布在包装的底部。每个焊盘上都粘有一个小小的焊料球,在PCB组装的焊料回流过程中,焊料球会融化并形成一个坚固的接头。

BGA引脚垫的间距根据设备引脚的大小和数量,从1.5mm到0.5mm。焊料球本身的直径范围从0.75毫米到0.3毫米。

随着复杂集成电路上引脚数的增加,bga之前使用的标准表面贴装封装变得不那么可取。为了支撑更多的引脚,这些传统的外围引脚封装必须增加尺寸,这在电路板上消耗了大量的空间。而且,随着包装尺寸的增大,它们开始遇到电气和制造方面的问题。然而,随着BGA包的转换,许多问题都得到了解决。解决的几个具体问题是:

尺寸:而不是依赖于零件的周长为组件引线,该BGA引脚均匀地分布在包装下面。与传统的双直插式或四平插式部件相比,这可以为相同数量的引脚提供更小的封装尺寸。

性能:随着引脚在BGA底部展开,连接模具到引脚的内部电线比DIP或QFP封装中的短得多。这些较短的连接降低了它们的电感和电阻,从而获得了更好的部件性能。

热阻:BGA中从模具到引脚的较短的导线也降低了热阻。这样可以使部件产生的热量更均匀地消散到电路板上,有助于冷却部件。

制造:没有通孔销或表面安装导致弯曲,BGA的处理问题比其他封装要少得多。在焊料回流过程中,BGA的焊料球也是自定心的,这有助于简化制造过程。

可靠性:BGA封装解决了制造高引脚DIP和QFP器件的可靠性问题。这些封装具有小型化的引脚宽度和间距,在组装过程中可以很容易地在引脚之间形成焊接桥。

然而,使用BGA包也会带来一些困难。例如,当BGA安装在电路板上时,如果没有x射线设备或其他先进的扫描工具,焊点的视觉检查几乎是不可能的。但是,这些问题是可以克服的,使用BGA包的好处远远超过它们的缺点。

接下来,我们将看看在PCB布局中放置BGA包时要记住的一些注意事项。

放置在电路板顶部的BGA封装。

BGA封装的组件布局PCB布局建议

您使用的BGA部件越复杂,您就必须提前计划,以便成功地将每个引脚路由到其相关网络。高引脚数bga的引脚间距为0.5mm,需要仔细规划为其所有网络设计逃逸路由模式。在开始路由跟踪之前,您需要对组件放置进行大量的预先考虑。

一如既往,开始你的放置平面布置图首先使用固定组件,如连接器、开关和其他IO设备。你还需要注意电路板的散热问题,以确保热运行的BGAs有足够的气流来保持凉爽。处理器和内存芯片需要足够靠近它们的板外连接器,这样它们就不必在整个板上运行很长的走线长度。与此同时,您必须为信号路径的所有部分提供足够的空间,使它们能够干净地匹配,而不会让它们的痕迹偏离太远才能到达它们。

当你开始你的位置,记得给你的BGA部件足够的空间,所有他们周围的路由。这些部分应该有很多旁路电容与它们相关联,并且它们需要直接放置在它们所连接的引脚旁边。接下来,作为信号路径的一部分的组件需要依次放置在信号的源和负载之间。这可能需要改变你的大部分位置,以适应这些部分,所以要准备好互动工作,以最终确定位置。

另一件要记住的事情是,除了良好的信号完整性,您还需要设计良好的电源完整性。这意味着放置不同的电力供应靠近它们供电的区域,而不允许它们的电路与bga的敏感数字电路混合。

以最优的方式安排部件位置后,是时候开始路由bga的网络了。

选择在PCB设计CAD工具中使用的过孔,用于在BGA包内和周围布线。

BGA包连接跟踪路由提示

要做的第一件事是规划从细间距表面安装组件(如BGA部件)的逸出路由或“扇出”。转义路由不仅仅是绘制一个短的轨迹并删除一个via;它必须与组件位置、层堆叠、信号完整性需求和路由密度一起规划。对于高引脚细间距bga,可能需要额外的板层或高密度互连(HDI)路由策略。然而,在承诺这一点之前,最好先与PCB制造商确认价格和他们建造HDI板的能力。

当涉及到将逸出轨迹和通孔路由出BGA时,首先从外层行开始。使用对角线路由,这些痕迹将是最简单的铺设。从那里,你可以开始工作通过你的方式通过大头针。对于具有较大引脚间距的bga,可以使用较短的走线段连接到衬垫旁边的通孔,这被称为“狗骨模式”。

较大的引脚间距bga也将允许您在衬垫之间进行路由。对于较小的pitch,可能需要使用平板Via,尽管这会增加电路板的制造成本。同样,请先与您的制造商确认他们能够为您制造的PCB技术水平和价格。以下是您将使用的通孔:

通孔:这是电路板中最常用的通孔。它们是用机械钻钻出来的,可以穿透整个木板,但对尺寸有最小限制。对于一个标准宽度的电路板,钻孔的最小尺寸通常不小于6mils。

盲孔和埋孔:这些通孔也是用机械钻制造的,但要么只能穿透部分板,要么在板的内层开始和停止。盲孔可以嵌入BGA衬垫中,盲孔和埋孔都需要在PCB制造过程中在板层压在一起之前钻孔。这些额外的步骤使盲孔和埋孔的制造成本更高,但成本的增加可能是致密板上的必要选择。

微孔:这些通孔是用激光制造的,比机械钻出的通孔要小,但由于尺寸较小,它们通常只跨越两层。微孔可以堆叠在一起或交错并排,以达到所需的结果。尽管它们的成本比机械钻孔孔要高,但它们无缝嵌入BGA衬垫的能力使它们成为细音高部件扇形的理想选择。

当您从BGA设备中布线时,请记住较高的引脚数部件将需要额外的电路板层。所有需要从引脚路由出去的过孔将占用您需要的跟踪的路由通道。你可能会发现自己不得不这么做添加另一个板层BGA上每两排针。

你可以做的一件事是帮助自己,咨询推荐的路由模式,许多部件制造商将包括在他们的组件的数据表。您还应该在PCB设计工具中设置设计规则和约束,以控制BGA路由的迹宽和间距的大小。我们接下来来看一下。

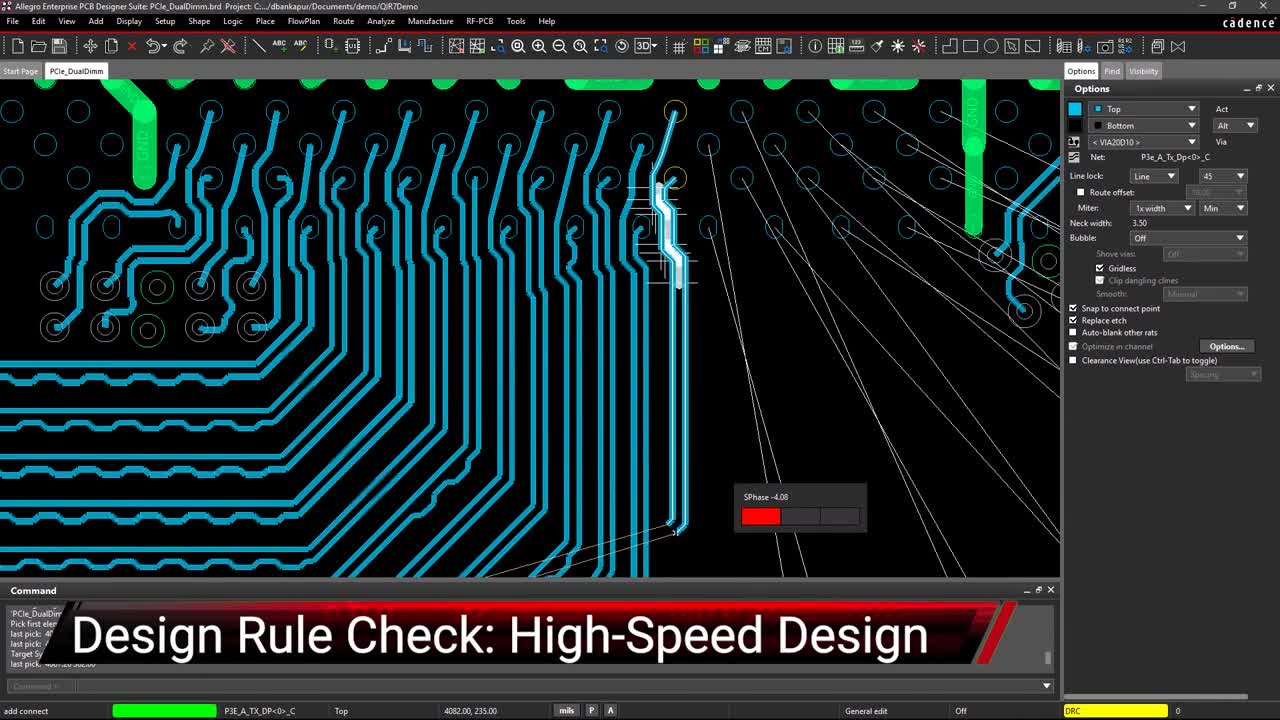

Cadence 's Allegro PCB Editor中的约束管理器显示分配给网络的通孔。

在PCB设计CAD工具中管理BGA设计规则

高速设计,将要求零件在BGA包通常有具体的高速的约束与他们相关。这将包括只能在某些层上路由的特定网络、必须一起路由的差分对,以及根据正在路由的网络而不同大小的跟踪。虽然设计人员可以很容易地跟踪其中的一些规则,但与路由BGA相关的数百种不同的网络和需求可能完全令人难以应付。这就是Cadence的Allegro PCB Editor等约束管理系统的帮助非常有用的地方。

上图中的约束管理器显示了分配给这个板上不同网的通孔。您不仅可以为网络和网络类分配不同的通道,还可以控制轨迹宽度和间距值。这将使您能够轻松地进出密集的BGA区域,而无需每次手动重置跟踪宽度和间距。还有许多其他技巧和技巧可以帮助您跟踪bga内部和周围的路由,您可以在本文中阅读更多有关它们的内容电子书.

如果您想了解更多Cadence如何为您提供解决方案,跟我们和我们的专家团队谈谈吧.