对高速信号完整性设计PCB布局

关键的外卖

信号完整性基础在印刷电路板。

布局建议打击在PCB设计中信号完整性问题。

PCB布局特点、功能和工具,将帮助你具有良好的信号完整性设计。

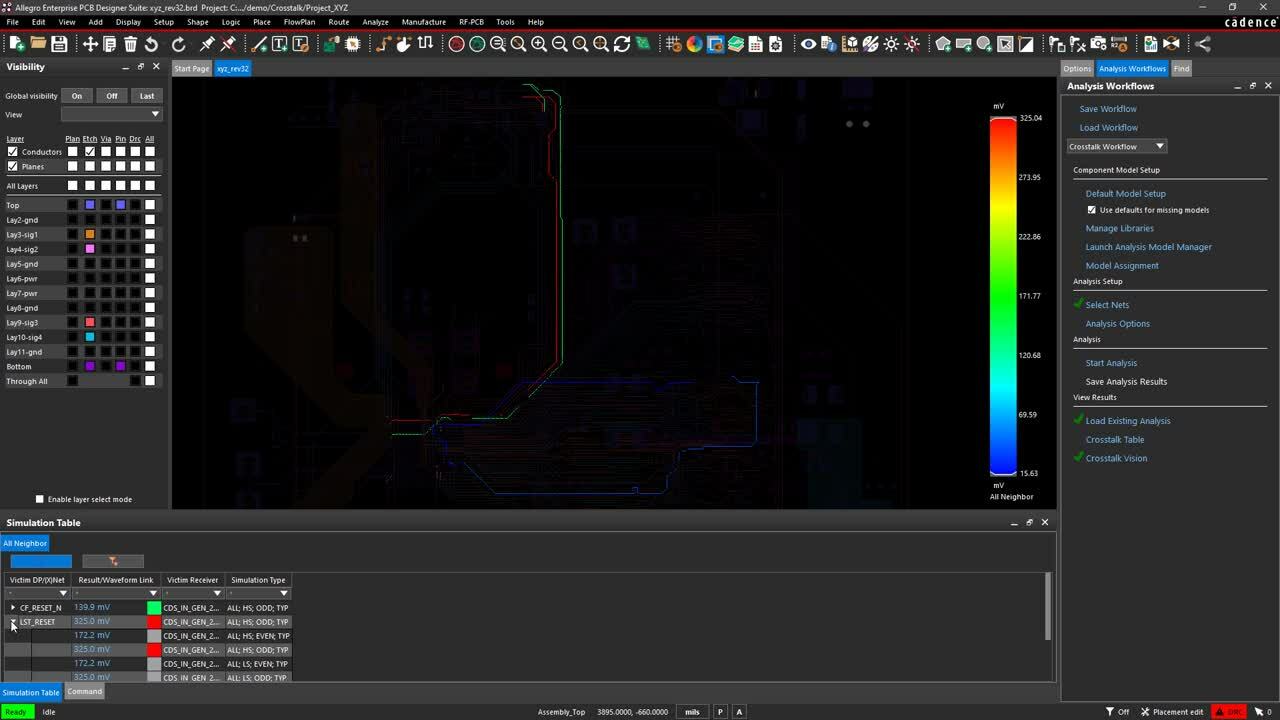

相声在PCB布局检查信号完整性验证

由于电路板信号速度的增加,需要把它们实现最好的电气性能。一次、PCB布局工程师不需要担心如何路由跟踪、信号速度足够慢不受物理布局的影响。然而,随着信号的速度增加,信号恶化的可能性由于高速布局差实践增加了。这种退化可以创建电路的时序和信号振幅水平问题,经常导致失败的电路由于误读的信号状态。

因此,一个好的PCB布局的目标是最小化信号退化尽可能多的数量。这可以通过精心配置板层分层盘旋飞行,组件的位置,所使用的路由策略。当使用这些策略时,设计师可以达到良好的高速信号完整性设计。这里有一些这种类型的布局的基本原则。

PCB信号完整性的基础知识

许多干扰会降低纯度在印刷电路板的一个信号,信号的速度越高,就越能受到这些问题的影响。这些干扰包括电磁耦合或串扰EMI,阻抗不匹配,和地面反弹。如果不加以控制,这些声音会降低信号的保真度,它可以传输错误。可怜的信号的完整性可以揭示在间歇难以诊断的问题,或者直接系统故障。另一个潜在的问题是原型和production-built板之间的区别。如果信号完整性是几乎没有边际的原型,它可能是完全不可接受的在生产单位。

它电路板工程师有责任确保他们的设计具有良好的信号完整性。然而,PCB设计者面临的困难是,这些干扰可以相互影响,并纠正一个问题可能会导致别人出乎意料地涌现。设计师需要记住,他们永远不会摆脱所有电路板上的信号完整性问题,总是会有一定程度的噪音或干扰。相反,设计师的目标应该是有效地管理干扰下的PCB布局使他们允许噪声预算设计。让我们看一些特定领域电路板上的信号完整性问题,如何控制好PCB布局实践。

一个好的PCB布局的关键是仔细考虑高速信号完整性的设计

在高速信号完整性设计布局建议

这里有四个主要的信号完整性问题,设计师需要注意和PCB布局的设计策略对于纠正他们。

无意之间电磁耦合的痕迹

当一个高速信号路由太近,信号脉冲可能会压倒了弱信号越强。之间的串扰信号会引起较弱的信号来模拟其目的而不是传输脉冲越强,系统中导致误解。这不仅可以发生在布线的痕迹,而且董事会层之间。

为了防止相声,电路板设计师应该考虑以下步骤在布局:

- 配置板层分层盘旋飞行位置地面飞机高速信号的路由层之间含有敏感。

- 也是好的交换方向在每个路由层侧向耦合的可能性降到最低,这层之间的串扰。

- 不要跑高速信号敏感,如时钟线,在长距离平行。

- 使用一个高速痕迹之间的距离增加。这些敏感的蚊帐需要超过它们之间的距离标准制造防范相声。

电磁干扰与其他信号

电路板,没有正确布局可以辐射EMI。长能像天线痕迹,痕迹存根或未通过桶也可以发出EMI。EMI的足病的“罪魁祸首”之一是缺乏一个明确的信号返回路径高速信号的参考平面。信号返回将徘徊董事会使用任何方法可以返回并创建一个很大的噪音和干扰而这样做。EMI可以伤害其他电路在黑板上或附近的硬件造成问题。

管理EMI电路板布局,设计师需要遵循以下基本原则:

- 电路板路线尽可能短的痕迹。

- 限制高敏感信号路由到一个板层。

- 把数字和模拟组件彼此分开两者之间为了保持隔离。

- 最重要的是,不要路线高速信号分割参考面,将会摧毁它的明确信号返回路径。

阻抗值的变化在高速的痕迹

最好的高速跟踪信号完整性,它必须有一个一致的和统一的跟踪和一个明确的返回路径。我们已经看到信号返回路径的重要性在一个参考平面,但维护的一致性跟踪本身一样重要。不受控制的痕迹可以改变其阻抗值从线的一端到另根据董事会的条件在哪里。没有阻抗控制,高速信号可能会被反射回源,当他们进入一个区域在黑板上,他们跟踪阻抗值的变化。

为成功阻抗控制路由,电路板必须正确配置根据计算基于这些指南:

- 阻抗控制路由需要局限于参考平面的层相邻。

- 之间的垂直间距控制阻抗跟踪和邻近的参考面必须包括在计算中。

- 绝缘的介电常数(Dk)电路板材料跟踪和参考面之间也需要整体阻抗控制的一部分计算。

- 最后,阻抗计算会给你正确的跟踪工作宽度的阻抗值,您需要为您的敏感高速跟踪路由。计算还需要指定跟踪或跟踪的横截面的厚度。

同步开关噪声(SSN)

不仅高速组件高低状态之间切换慢速度远远超过操作设备,但也有通常比有更多的人在一个电路板。有这么多设备快速切换状态,电压不得返回所有的方式回到他们参考地面,而上面的“反弹”。如果一个低电压状态反弹高于地面,低状态可能会被误解为一个高状态,而导致错误的或双开关。这种情况可能会影响电路的正常运行。此外,没有信号返回一直到低的状态,有一个意想不到的增加电流的跟踪,这创造了噪声信号。

停止同步开关噪声或地面反弹,这里有一些布局策略,可以帮助:

- 为每个设备使用足够的电容器来稳定电压和吸收地面反弹。

- 放置去耦电容的设备尽可能销,他们被分配到的力量。这将有助于遏制当前峰值在设备切换。

- 每个地面销连接在设备上应该有自己的地平面,不会与其他地面连接链接在一起。

- 在整个电力和地面连接功率输出网络(生产)应该有广泛的痕迹,通过增加电流的流动,减少的电感量。

确定这四个区域的信号完整性问题,让我们看下一个在你的设计的一些功能的工具,可以帮助您改善高速信号完整性设计。

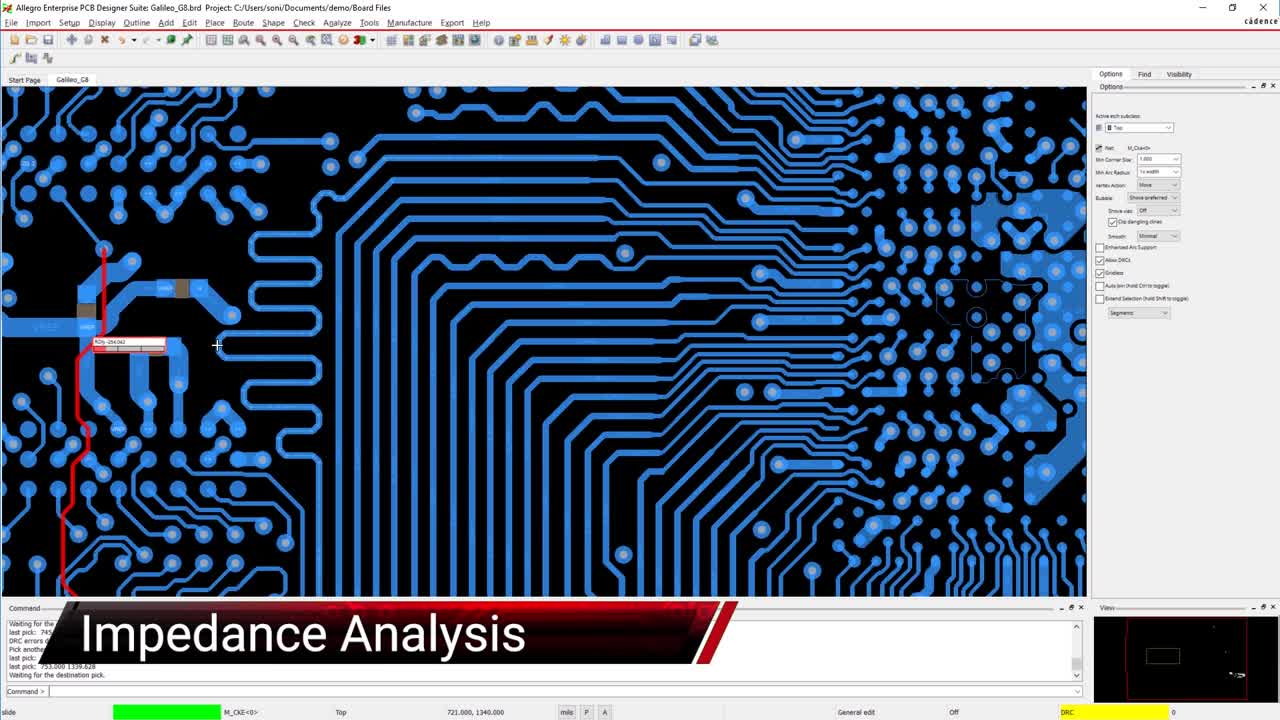

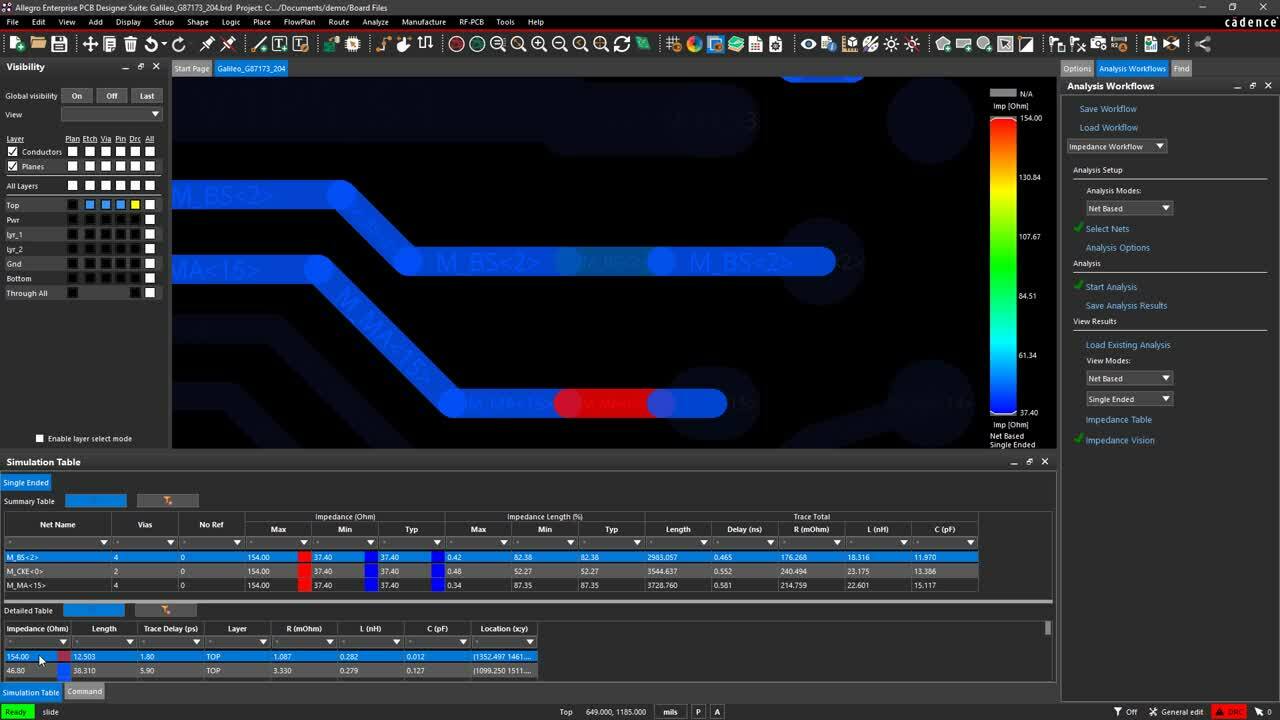

阻抗检查在节奏快速的PCB编辑器

有用的布局工具功能

今天,PCB设计工具有许多有用的特性和功能帮助布局设计者验证实时高速的信号完整性设计。这允许许多噪音的问题得到解决之前建立的第一物理原型。节奏的快板PCB编辑器是一个很好的例子,这些信号完整性分析工具:

相声:发现和纠正传统上属于调试电磁耦合问题的物理原型。这种串扰的方法检测通常需要大量的时间和使用专门的工具。然而,随着串扰分析工具构建到CAD系统,布局设计者可以解决大多数的耦合问题在发送之前他们的设计制造。

电磁干扰:正如我们上面提到的,EMI辐射的主要来源之一,在电路板设计不良信号返回路径。即使是最好的设计师可能并不总是拥堵点地区的地平面上将扰乱返回路径。幸运的是,返回路径分析工具的PCB布局CAD系统可以很容易地找到设计师和报告这些问题。

阻抗:成功impedance-controlled路由、电路板需要建立正确的板层分层盘旋飞行,跟踪宽度和间距。大多数CAD系统为这个目的,提供一个阻抗计算器和节奏更进一步阻抗分析工具在上图中可以看到。这给了设计师的能力实时检查的路由是否布置实际上是所需的阻抗值。此外,内置的反射分析工具将帮助设计师发现潜在的信号反射领域由于阻抗不匹配提供了额外的保护信号完整性问题。

权力的完整性:正如我们所见,控制地面反弹和其他电源完整性问题需要勤奋的设计生产。即使是一个小问题,比如金属在热连接数量不足,足以产生噪声和降低董事会权力的完整性。等在线工具IR降的分析功能快板,设计师可以快速发现问题与他们的生产设计和改正。

这些布局和布线后的分析工具可以是一个真正的救命稻草PCB设计者和高速设计创造。另一个巨大的帮助在制定董事会与正确的宽度和间距值,和所有这些其他有用的特性一样,急速地约束经理也覆盖了。

设计规则组件放置重要的制造业和信号完整性

这一切开始的设计规则

好的信号完整性设计高速PCB的布局从一套成熟的开始设计规则和约束。如果做得对,这些将管理跟踪宽度和间距为不同类型的信号,包括数字、模拟、高速数字和模拟,差分对,高速拓扑,和,当然,不同的权力和地面的要求。他们还将控制路由层,这些层的路由方向,和特殊区域收缩痕迹宽度,在BGA等。

设计规则和约束也可以控制和单个组件或组件组被放置的地方。也可以设置捕捉潜在的制造和装配问题,丝网印刷错误,和许多其他问题可以延迟或减缓电路板的制造。

高速设计策略的更多信息,看看这个电子书从节奏。

如果你想了解更多关于节奏是如何对你的解决方案,跟我们的专家团队。