DDR路由概述

关键的外卖

DDR内存路由的重要性,以及您应该了解的一些关键点。

从转义路由和终端到路由和使用HDI设计,这些技巧将帮助您进行下一个DDR内存设计。

你需要先进的PCB设计工具来完成正确的工作。

通过实时平视显示,轻松满足您的DDR网的定时规格。

过去,计算机被认为是一个单一的物体或设备,具有特定的用途,有点像插入烤面包机或洗衣机。尽管我们知道几十年来情况并非如此,但大多数人仍然不明白他们每天实际使用的计算能力有多少。我们所有的智能手机、汽车系统和物联网设备都依赖于计算能力来完成工作,如果没有DDR内存,这些都不会发生。

从20世纪90年代末开始,开发了DDR内存标准,以提供更快地访问存储在内存中的数据。自引入以来,DDR内存每5年左右就会进行一次增量改进,以提高其性能和功能。虽然DDR3和DDR4仍在使用中,但随着DDR5的推出,我们现在进入了一个新的性能标准。

为了处理这种级别的性能,印刷电路板必须精确地设计和布局,以适应DDR存储器的高速要求。让我们更详细地了解这些要求是什么,以及如何在PCB上成功实现DDR路由。

DDR路由是什么?为什么它很重要?

计算机内存通过在CPU的时钟周期内发送和接收信号与处理器一起工作。最初,这种交换在称为单数据率(SDR)内存配置的每个时钟周期中完成一次。为了提高数据交换的速度和性能,信号现在每个时钟周期发送和接收两次。这种双数据率(DDR)内存已经取代了SDR,现在是内存配置的标准。

DDR已经使用了20多年,在这段时间里,它经常更新以提高速度和性能。目前使用的版本是DDR3和DDR4,最近有DDR5可用。任何使用内存的印刷电路板设计都很可能在其中使用某种版本的DDR内存标准。PCB设计人员需要在内存电路的路由中使用精度,以满足性能规范。

用于定时信号的蛇形跟踪路由

DDR路由中的一些关键点,都是关于时间的

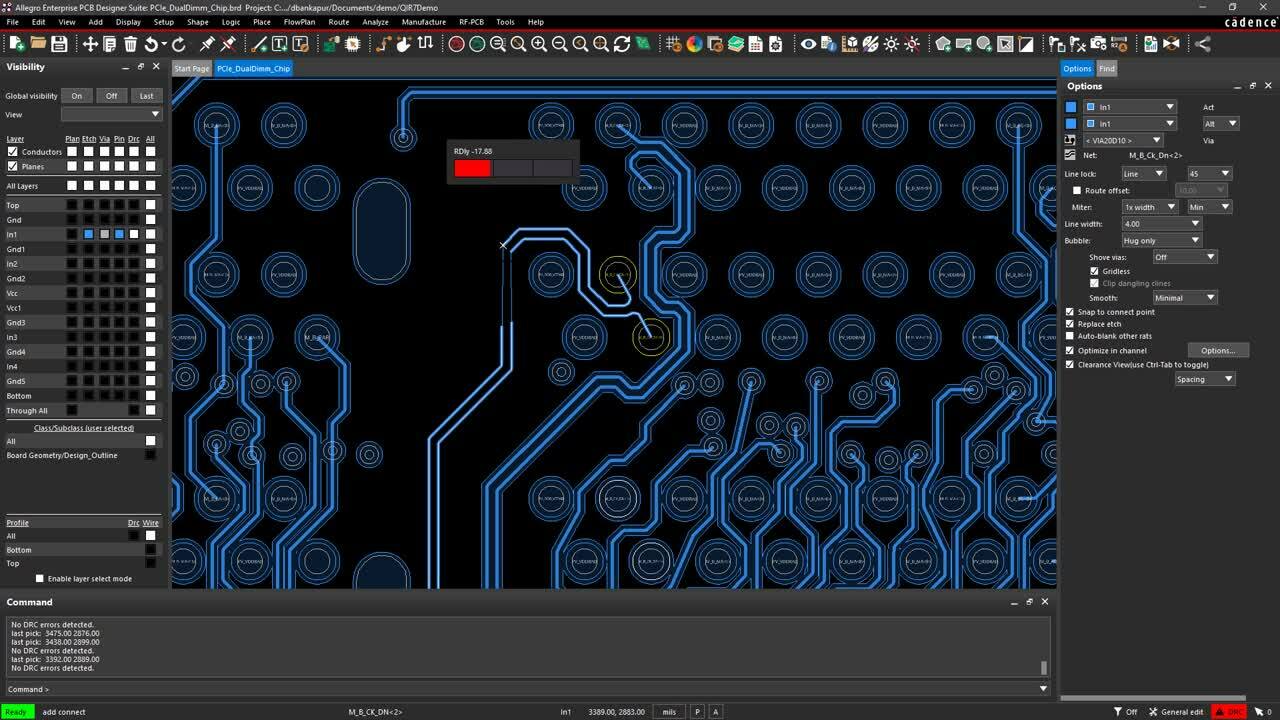

在路由DDR内存中最重要的事情是满足它的定时规范。需要对单个信号进行计时,以便在与之相关的时钟线的上升沿和下降沿捕获数据。由于电信号不能加速,控制这个时间的唯一方法就是减慢它们的速度,使它们在适当的时刻同时到达。这是通过在一种被称为蛇形布线的设计方法中增加轨迹的长度来实现的,您可以在上图中看到示例。

这些规格必须满足内存的功能,因为它是打算。对于PCB设计人员来说,使用CAD软件的设计约束来帮助他们达到路由的这个时间标记是很重要的。这些约束可以设置为使用特定的净长度,也可以自动路由蛇形图案,以便将轨迹路由到正确的长度。

然而,与任何高速设计一样,所有这些约束都必须插入到PCB的整个设计参数中。例如,由于靠近地平面,在板的外部层上路由的走线与在内层上路由的走线具有不同的定时特性。在只有一个平面与之相邻的外部层上的微带路由配置与夹在两个平面之间的内层路由的条带线配置的性能不同。PCB设计人员在规划DDR路由以实现最佳电路性能时,必须考虑所有这些因素。随着DDR的每个新版本的引入,定时规范变得越来越严格,要求路由更加精确。

现在让我们更深入地研究DDR路由的细节。我们将首先从BGA转义路由和传输线中匹配终端的需求开始。然后,我们将研究DDR3和DDR4路由准则,以及PCB设计中的一般DDR路由技术和HDI路由。

DDR路由:循序渐进

DDR内存路由不仅仅是连接跟踪的问题。路由必须从最初的转义路由一直到最后仔细规划。

转义路由出一个大的BGA包

第一步是设计BGA转义路由

路由从组件在单板上的良好位置开始,DDR内存路由也不例外。下面是一个推荐的布局组件的顺序:

固定组件,如连接器

主动元件(为优化信号路径、冷却考虑等而放置)

BGA上的外排引脚,并将它们从零件上布线

BGA内部引脚的常规转义路由(通常是狗骨模式)

您可能会发现高密度部件可能需要在衬垫和微孔中使用通孔。

这使你能够学习更多关于BGA转义路由的信息.

不要忽视你的匹配终端的正确位置和路由

即使你的迹线看起来很短,它们也会给你的高速数字电路增加一些延迟,而这些延迟会带来反射问题。如果没有正确地终止迹线,电压波可能沿线路向下传播,与原始信号波碰撞。根据反射波的极性,这既可以抵消原始波,也可以增加原始波。当线路的阻抗因通孔、连接器和迹根而改变特性时,就会发生这些问题。为了解决这个问题,串联端应添加到线路上,以增加等于特性阻抗的电阻。

欲了解更多信息在匹配的终止上.

DDR3路由指南

DDR3标准于2007年推出,以取代DDR2,至今仍在使用。一个DDR3 DIMM封装可以有240个引脚,这意味着有很多高速线路需要路由。有这么多线路要路由,空间将是有限的,并可能导致串扰,这可能会导致电路的信号完整性问题。与任何DDR路由一样,需要严格控制关键线路(如数据、地址、时钟和控制信号)的跟踪长度,以获得最佳性能。

这里有更多的细节DDR3路由指南.

一个差分对路由的例子

DDR4路由指南

没有什么是保持不变的,但是为了满足先进的DDR4标准,需要改变设备架构。DDR3使用240引脚DIMM封装,而DDR4将引脚数量增加到288个。这导致了其性能和速度的改进,同时降低了所需的电压量。这也增加了PCB设计的工作量。除了在路线上增加更多的关键线条外,对精确位置和路线技术的需求也增加了。

这里有更多的细节DDR4路由指南.

将DDR路由技术纳入您的设计

要成功地路由DDR内存路由,您的设计必须具有最佳的组件位置,并且必须有适当的路由计划。会有不同需要路由拓扑您需要了解的不同版本的DDR内存。虽然t -拓扑路由方法在旧版本的DDR内存中工作得很好,但它不能处理DDR3和DDR4的更高信号速率。相反,飞越拓扑通过菊链模式提供了更好的成功,这也极大地有助于提高信号完整性。

如果你想了解更多关于DDR路由技术的细节.

高密度互连和HDI路由的注意事项

如果您正在设计具有DDR内存路由的电路板,那么您可能正在使用高密度互连(HDI)设计。这意味着为了能够挤进所有的电路,你将在更薄的基片上使用更薄的层,更小的走线,过孔和衬垫。当HDI设计正确时,您可以获得许多好处,例如除了创建更小的电路板外,还可以减少EMI。一个成功的HDI设计意味着PCB设计师需要更多的关注和注意细节。

你可以找到更多关于HDI路由的信息.

印制电路板上的密集布线

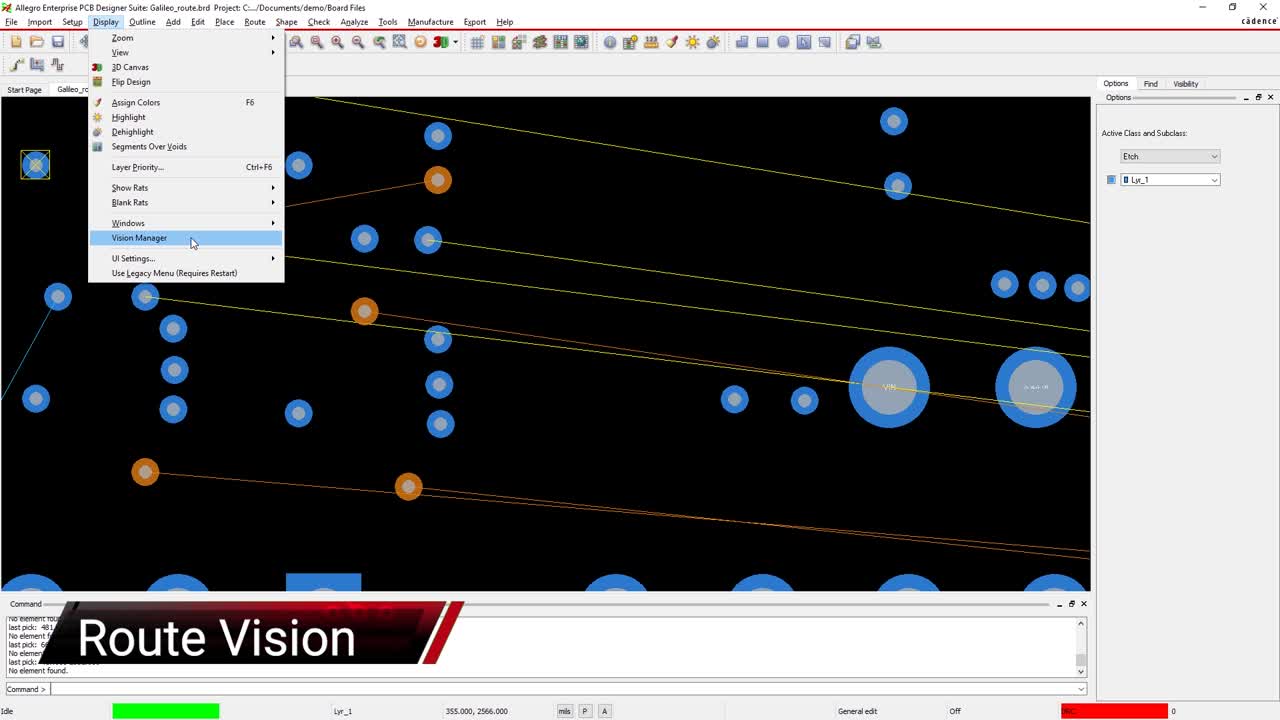

适合DDR路由的PCB设计工具

为了成功路由DDR内存配置,您需要PCB设计软件为您提供成功所需的工具。这不仅包括创建组件占用并将这些部件放置在电路板上,还需要一组完全可配置的设计规则和约束,以便指定DDR信号的长度和飞行时间。然后,您需要最先进的路由功能,以正确的长度放入跟踪。

PCB设计工具像这样的高级DDR路由已经可用,以保持您在竞争浪潮中的领先地位。Allegro PCB Designer拥有我们一直在谈论的能力,并将为你完成工作。

如果您想了解更多Cadence如何为您提供解决方案,跟我们和我们的专家团队谈谈吧.