PCB布局中如何规划DDR路由

关键的外卖

使用DDR路由的规则、约束、占用区和过孔设置设计。

路由DDR内存的注意事项。

您的PCB设计工具如何帮助您实现DDR内存路由。

DDR4内存条

20多年来,DDR存储器一直是PCB设计中不可或缺的一部分。最初的DDR内存很快被DDR2取代,然后是DDR3,最后是DDR4。然而,随着DDR存储器的每一次新迭代,PCB设计的挑战变得更加复杂。引脚数量增加了,设计限制也变得更严格,导致PCB设计师需要完美地布线大量的网络。

成功路由DDR内存的关键是在开始之前做好准备。这意味着从一开始就为需要做的路由类型规划PCB设计。电路板材料、层堆叠、组件放置、通道类型和路由拓扑都必须提前计划好。以下是关于如何在下一次PCB设计中规划DDR路由的更多细节。

为成功的DDR内存路由设置设计

准备设计带有DDR内存路由的单板的第一步是规划单板的层数和配置。由于您将处理高速电路,您可能需要考虑标准FR-4以外的其他电路板材料。但最重要的部分是配置你的设计层为了董事会。尽管可以将密集路由压缩到更少的层中,但这很可能不是实现信号完整性的最佳配置。由于设备的高密度,您可能会在DDR路由堆栈中看到12层,并且需要条带线和双条带线层配置。

下一步将是为设计建立规则和高速约束。很多规则应该在设计之初就包含在原理图数据中。不过,您很可能会发现需要将更多规则加载到布局数据库中。在这里,当您收集和组织设计规则和约束时,与设计团队的所有成员合作将获得回报。由于您的许多设计可能具有相似的特征和功能,因此保持一个良好的设计通常是有帮助的设计规则和约束库从以前的设计中。这将帮助你减少花在这项任务上的时间。

与任何设计一样,在开始之前,您将需要花费大量的时间来确保PCB组件占地面积和地面模式是正确的。这将为您节省大量的时间,使您不必纠正和更新一开始就不正确的部分。这样的错误不仅会削弱你的计划,而且如果更新的部件不再适合你已经完成的位置和路由,它可能涉及大量的返工。

您还必须为以前没有使用过的设备(例如DDR内存部件)创建新的占用空间。这就是你的网上图书馆资源可以提供很大的帮助,例如Cadence Allegro PCB设计工具中的统一部件搜索功能。有关使用PCB库符号的更多信息,请参阅原理图符号规则在这本电子书中。

在Allegro的约束管理器中设置差分对

如何规划DDR路由使用最佳位置和通过转义

好的DDR路由计划首先要求您有良好的组件位置。你之前使用的高速设计方法在这里仍然很重要:

信号路径:在高速设计中,您需要考虑敏感电路的整个信号路径,而不是只考虑点对点连接。这意味着从原理图开始依次放置部件,以保持从驱动器到接收器的整个路径,以及中间的任何部件尽可能靠近。

内存设备:这些部件需要放置在一起,以尽量减少它们之间的路由,并保持它们分组。它们还应该按顺序排列,从最低的数据位开始,以最高的数据位结束。

路由通道:使用DDR内存将路由许多网络,您需要有意地将您的部分放置到您将需要的预期路由空间中。这样做也会为通过转义模式提供足够的空间。

敏感电路:给敏感的高速电路足够的空间来隔离干扰。这种噪声可能来自其他信号,如时钟或电源电路。

旁路电容器:为了保持存储电路中的信号完整性,您将放置更多的旁路电容来稳定参考电压。确保为这些盖子留出足够的空间,这样就不会占用已经预留的路径和逃生通道的空间。

您可以通过阅读本电子书找到关于放置组件的其他详细信息成功安装和放置的步骤从节奏。说到转义通道,要成功地路由DDR内存,您需要在布局中有一个良好的转义通道计划。

首先,你必须决定使用哪个通道;穿透孔,盲的,或埋的。你甚至可能想使用微孔来给自己更多的空间,但要注意这样做的成本增加。你们很多人通过逃将从高引脚球栅阵列(BGA)零件。引脚间距越小,你就越想在BGA衬垫中使用通孔。这将帮助您排除BGA模式,但同样需要在制造复杂性和成本之间进行权衡。这里有一个很好的参考资料,那就是咨询DDR组件的供应商,找出他们推荐的通道转义路由模式。

具有调优轨迹的高速路由

DDR内存路由注意事项

现在,您已经准备好开始规划可供您使用的不同路由策略DDR内存路由.路由的拓扑结构将由所处理的信号组决定。雏菊链路由用于地址和控制路由,而点到点路由用于敏感电路,如差分对。然而,对于DDR路由,有一些特定的拓扑需要注意:

T-Topology:这用于旧的DDR路由,因为它无法处理DDR3和DDR4引入的更高的信号速率。T-Topology将时钟、命令和地址信号以分支方式从控制器路由到存储设备,同时直接连接数据线。

逐飞路由:逐飞路由不同于t型拓扑,因为它将时钟、命令和地址以链的形式从控制器路由到不同的存储设备。数据线仍然像在DDR2中那样直接连接。

翻盖:在这种配置中,存储设备位于单板的前面和后面。这样可以减少使用的单板空间,但会使路由更加复杂。然而,如果成功地做到了,这种策略可以通过在板的顶部和底部的设备之间共享过孔来帮助您的路由。

您计划采用哪种拓扑取决于电路和电路板布局的需要。飞掠拓扑比t型拓扑有了很大的改进,因为它们支持更高频率的操作,并减少了路由量,从而提高了信号完整性和时序。要进一步了解高速设计问题,如噪声和定时问题,请看看这个电子书从节奏。

由于DDR内存中的数据速率翻倍,为了满足设备的性能规格,精确路由跟踪长度变得非常重要。由于每个时钟周期能够发送和接收两次信号,数据必须在其时钟的上升沿和下降沿捕获。要做到这一点,必须精确地控制电路定时,这是通过控制路由模式的迹长来实现的。关于PCB路由的其他提示和技巧,请查看本电子书成功设计之路.

在约束管理器中设置网络组上的最小/最大传播延迟

你的工具如何帮助你更上一层楼

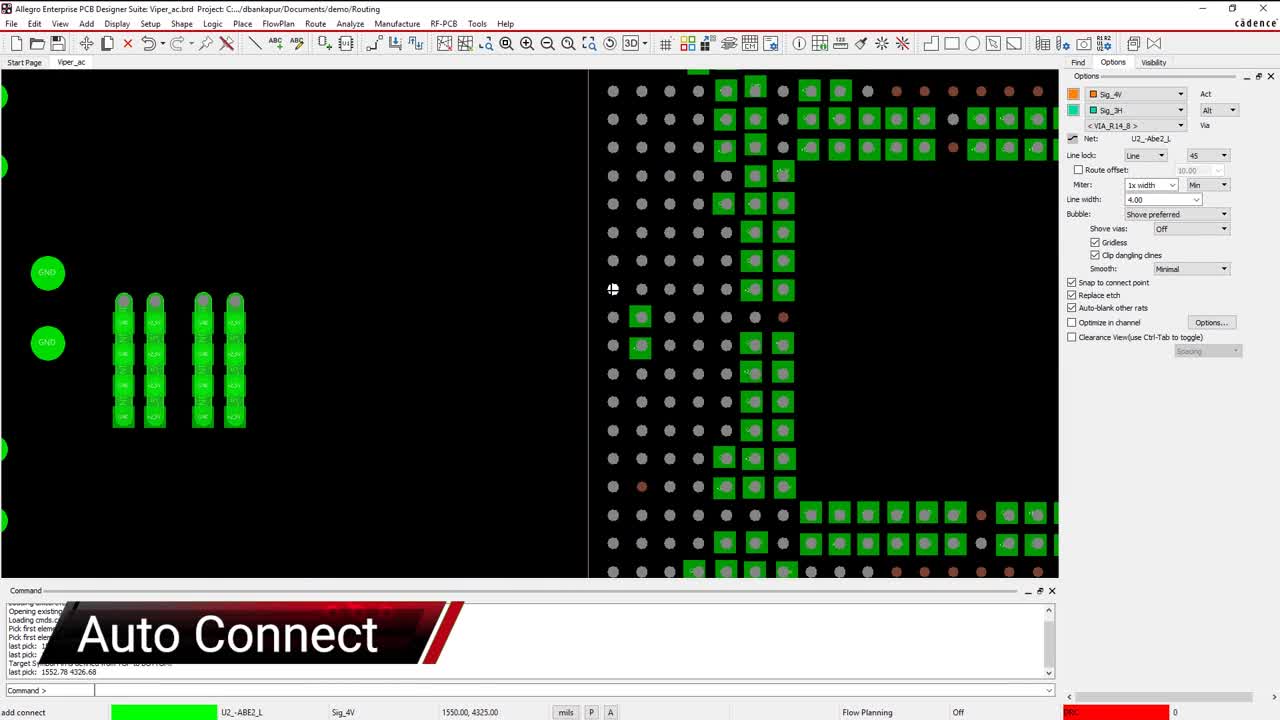

当你准备设计一个带有DDR路由的电路板时,有很多事情需要计划。另一种帮助您为这一级别的设计做好准备的方法是使用具有内置高级路由特性和功能的PCB设计工具。你需要能够轻松地设置你的规则和设计约束正如我们上面提到的,拥有多个功能来帮助你手动和自动路由是很重要的。在路由DDR内存时,按颜色分隔不同的内存组也很有帮助,当然还需要在设计系统中内置模拟和分析工具。

所有这些帮助您进行DDR路由的特性都可以在最好的情况下找到PCB设计系统.其中最先进的是Allegro PCB Designer从节奏。使用Allegro,您不仅可以获得当前DDR路由考虑所需的完整设计系统,而且还可以为下一级别的DDR内存路由以及更高级别的路由做好准备。

如果您想了解更多Cadence如何为您提供解决方案,跟我们和我们的专家团队谈谈吧.