硬件描述语言:vs Verilog硬件描述语言(VHDL),他们的功能使用

关键的外卖

●了解硬件描述语言。

●更好地理解hdl的重要性。

●了解更多关于不同类型的硬件描述语言。

硬件描述语言(VHDL)提供更快更准确的设计。

语言,大多数指标,是任何文明社会的基础。电子产品领域,这在某种程度上是自己的社会,还利用特定于其成员的语言。两个领域的硬件描述语言VHDL和Verilog。都被认为是通用的数字设计语言,每一个细微的差别和优势。

硬件描述语言(hdl)是什么?

高密度脂蛋白确实是类似于编程语言,但并非完全相同。我们利用编程语言构建或创建软件,而我们使用硬件描述语言来描述或表达数字逻辑电路的行为特征。

我们利用hdl设计处理器,主板,cpu(即。电脑芯片),以及其他各种数字电路。

硬件描述语言(VHDL)是什么?

非常高速集成电路硬件描述语言(VHDL)是用来描述硬件描述语言。它是利用在电子设计自动化表达混合信号和数字系统,如ic(集成电路)FPGA(现场可编程门阵列)。我们还可以使用硬件描述语言(VHDL)作为一种通用的并行编程语言。

我们利用硬件描述语言(VHDL)写文字描述或表达逻辑电路模型。如果文本模型逻辑设计的一部分,该模型是由合成处理程序。下一步过程中集成了一个模拟程序来测试逻辑设计。在这一步中,我们利用仿真模型描述接口的逻辑电路的设计。我们将这组testbench仿真模型。

通常情况下,硬件描述语言(VHDL)模拟器是一种事件驱动模拟器这意味着我们将每个事务添加到事件队列为特定的预定时间。例如,如果一个信号赋值后发生一纳秒,我们将事件添加到队列时间+ 1 ns。虽然零延迟是允许的,它仍然必须安排,这些场景我们利用δ延迟。

注意:δ延迟表示一个无限小的时间步。

硬件描述语言(VHDL)的功能

这些模拟交替之间的两种模式:

语句执行:在这种模式下,触发语句评估。

事件处理:在这种模式下,处理队列中的事件。

虽然有一个内在的相似性在硬件设计,硬件描述语言(VHDL)过程,可以进行必要的住宿。然而,这些过程不同语法(Ada)并行处理的任务。

类似于《美国残疾人法》的颁布,硬件描述语言(VHDL)是一个预定义的编程语言的一部分,另外,是不区分大小写的。然而,硬件描述语言(VHDL)提供了各种功能不可用Ada,例如,一组广泛的布尔操作符包括也和nand闪存。这些附加功能使硬件描述语言(VHDL)的精确表示操作的硬件。

硬件描述语言(VHDL)的另一个特点是它有文件输出和输入功能,您可以使用作为文本处理的通用语言。虽然,我们通常看到他们在使用数据验证模拟testbench或刺激。特定的硬件描述语言(VHDL)编译器构建可执行的二进制文件,支付的选项使用硬件描述语言(VHDL)写一个testbench功能验证设计利用宿主计算机上的文件比较预期的结果,用户交互,并定义刺激。

注意:艾达是一个静态类型,结构,面向对象,和必要的高级编程语言;这是一个扩展,来源于帕斯卡和其他编程语言。它的名字,艾达,指Ada Lovelace (Ada金;1815 - 1852),浪子的伯爵夫人,我们的信用是第一个计算机程序员。

硬件描述语言(VHDL)的优势

硬件描述语言(VHDL)的关键优势,对于系统设计利用率,是它允许的行为基本系统验证和建模的合成工具翻译的设计转化为实际盖茨和电线(硬件)。硬件描述语言(VHDL)项目也可移植,这意味着您可以为一个元素生成一个项目基地和基地,然后在另一个端口元素如VLSI、各种技术。

使用硬件描述语言(VHDL)提供用户并发系统描述。硬件描述语言(VHDL)是一种数据流语言,这意味着它可以同时考虑每个语句执行。这是直接与程序计算语言(如C、汇编代码,和基本的。这些语言语句的顺序,顺序和单指令。

硬件描述语言(VHDL)是更有利的好处之一,其项目是多用途;创建项目一次,您可以利用计算块在不同的其他项目。这意味着你有能力改变,如参数、元素基础,内存大小,块组成,互连结构和能力。

Verilog是什么?

我相信你知道,Verilog硬件描述语言。它雇佣了一个文本格式来描述电子系统和电路。在电子设计领域,我们用Verilog为可测试性分析,通过仿真验证故障分级,逻辑综合和时序分析。

Verilog以来也更紧凑的语言更多的是一个实际的硬件建模语言。因此,您通常编写更少的代码,它抒发C语言的比较。然而,Verilog上级对硬件建模以及低水平的编程结构。Verilog硬件描述语言冗长不如,占其紧凑的性质。虽然硬件描述语言(VHDL)和Verilog相似,他们之间的分歧往往超过他们的相似之处。

Verilog HDL是IEEE标准(IEEE 1364)。收到它在1995年首次出版,随后在2001年修订。Verilog SystemVerilog, 2005年修订,是最新出版的标准。我们叫IEEE Verilog标准文档LRM(语言参考手册)。目前,IEEE 1364标准定义了PLI(编程语言接口)。

注意:照明灯具是一种集体的软件例程之间的双向接口,允许其他语言如C和Verilog。

硬件描述语言(VHDL) vs Verilog

像大多数的选择必须制造领域的电子产品,它通常围绕着功能优势。在vs Verilog硬件描述语言(VHDL)的情况下,它也不例外。其中一个操作优势硬件描述语言(VHDL)相比原来的Verilog硬件描述语言(VHDL)的完整的类型系统。该系统提供设计师编写更加结构化代码的能力,这是特别有用如果宣布记录类型。总之,有不同意见的语言优越,但是,它真的只是归结为个人偏好。

Verilog提供更快、更精确的设计和验证。

值得庆幸的是,与我们的PCB设计和分析概述页面,你一定会有你的设计师和生产团队合作对利用适当的HDL的贵公司的设计和制造的需要。开云体育官方登录如果你的公司需要开云体育官方登录更多信息的使用硬件描述语言(VHDL)或Verilog如何受益公司的设计,然后我们的看法有什么新鲜事在快板PCB设计页面。

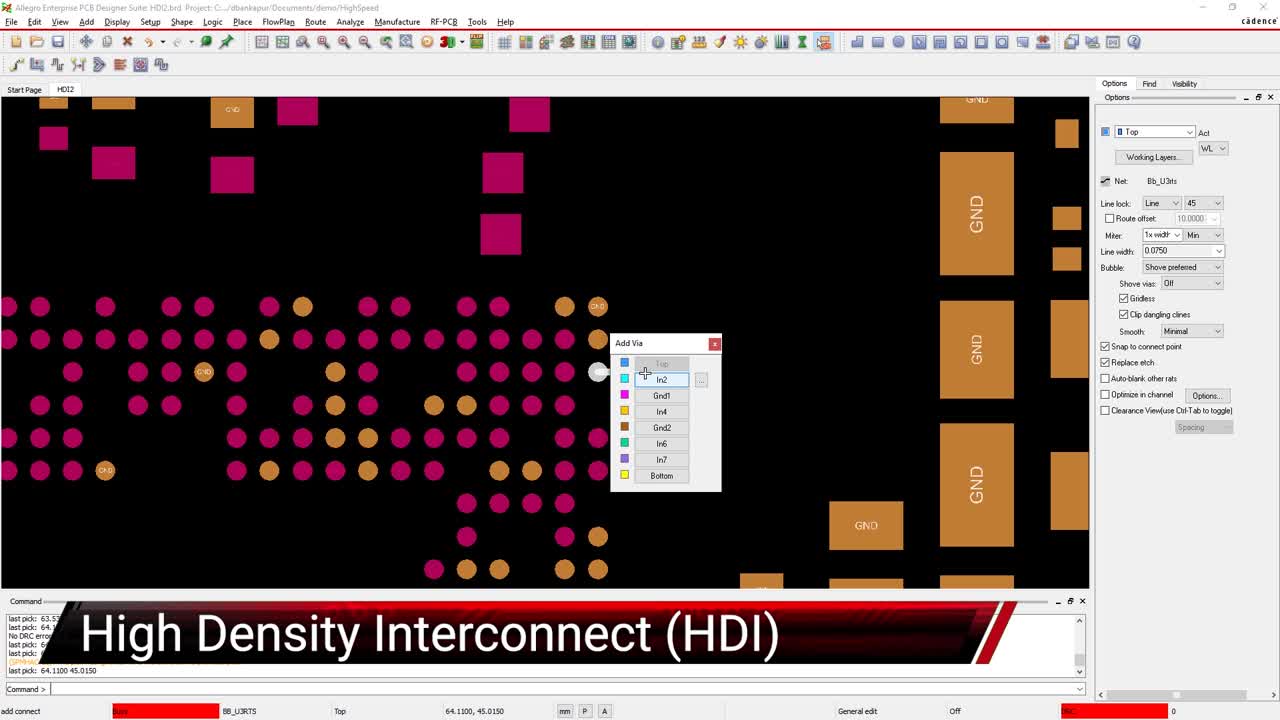

无论你是利用单面纸板或多层设计,你需要正确的PCB布局和设计软件。快板PCB设计者和节奏的全部设计工具套件可以帮助您创建设计验证组件模型并分析其功能的各个方面。您还可以访问一组工具MCAD设计和准备生产。

如果你想了解更多关于节奏是如何对你的解决方案,跟我们和我们的专家团队。对相关话题或观看视频看看新的设计和分析工具与我们的套件,订阅我们YouTube频道。