约束管理阻抗控制高速设计

关键的外卖

- 阻抗不匹配导致反射和并行信号网的失调,导致一些错误在一个接收器。

- 迅速确定阻抗违规需要约束经理您的PCB设计工具。你可以设置阻抗限制和公差设计约束。

- 布线后仿真工具可以用来检查网不符合阻抗约束和识别领域设计应该改变。

使用约束管理阻抗控制和发现反射

跟踪阻抗控制是一种简单的正确大小的痕迹。当一个跟踪孤立的考虑,其阻抗将会有一个明确的价值。然而,当把另一个跟踪或导体附近的阻抗跟踪将不同于其设计价值由于意想不到的耦合。这恼人的事实产生阻抗变化沿着一个互连,和极端的输电线路和接收机之间的阻抗不匹配会导致信号反射。

虽然你可能路由PCB布局与最佳实践和设计跟踪宽度仅用于路由,你仍然可以是一个互连阻抗变化的风险。这就是constraint-drive设计提供了检查你的董事会的利益对你的设计约束你路线布局。如果你把一个老,您需要检查阻抗在批次,您可以运行一个批处理侵犯刚果民主共和国和浏览阻抗。

当你准备纠正任何阻抗错误在你的董事会,Sigrity布线后仿真特性使您能够分析在单端阻抗和微分互联。你也可以点反射在特定地点互联,如通过或连接器的转换。这是这是如何工作的快板的PCB布局工具和Sigrity分析功能。

定义约束的阻抗控制

阻抗控制都是关于确保痕迹的几何在PCB在每个互连是一致的。这适用于单端和差分对。这些约束需要遵守你的定义高速信号标准。反过来,这些信号标准取决于您选择的组件或接口你设计的类型。

PCB设计软件被设计成适应确保您可以定义任何物理和电气约束来遵守DFM需求和信号标准。快板的设计工具允许您定义所需的阻抗值和公差使用快板约束管理器。这个工具可以访问在快板PCB设计者或快板Sigrity SI。

在即将到来的示例中,我们将看看如何定义和检查阻抗约束网的一组现有的布局。四网我们想检查如下所示。这四个网是DDR3的一部分数据总线和需要34欧姆阻抗定义。在这里,我们会检查这些痕迹电平标准下的阻抗在一定范围内,过度思考不发生在这些痕迹。

四个阻抗控制网进行分析。

定义约束

开始定义的限制,我们需要决定如果约束定义在单个网,或网组。快板PCB设计允许用户指定网一个群体,和相同的设计规则集可以分配给整个集团。注意,你不需要指定一个净一组;净可以有它自己的设计规则和约束。所有设计约束可以访问、查看和编辑在急速地约束管理器。

访问快板约束管理器和定义约束你的董事会,打开你的.BRD文件快板Sigrity SI。单击设置菜单和导航到约束→约束管理器。当你打开约束管理器,您可以访问组和网络电子约束的面板在屏幕的左边。

设置为净组阻抗约束,打开电气约束集选项并导航到路由→阻抗。下图显示了两个净组中定义。作为网络组织的一部分DDR3接口,跟踪在这个界面的阻抗应该设置为34欧姆。阻抗宽容已经被设置为5%。

为净组阻抗约束。

四个痕迹我们想检查并不是这些网络组织的一部分,但是我们可以分配这些痕迹这些网络组织,如果我们想要的。另一个选项是定义阻抗约束这些痕迹单独在电气约束集。应用规则,简单地向下滚动到净截面内的电气工作表约束管理器。当你打开路由→阻抗部分中,您将能够看到所有网,他们所属的团体。

如果你想指定一个净一套电气间隙,简单地打开下拉菜单中引用电气C组列并选择所需的电气间隙。现在,我们将目标阻抗值分配给个人网我们想检查。下图显示了目标阻抗将34欧姆阻抗为5%。一旦定义目标阻抗值,我们可以看到,网络是用红色标记。如果净不立即国旗,仅仅从工具栏运行设计规则检查(选择更新工具菜单下的刚果民主共和国)。

阻抗约束个人网。

在上面的图片中,这四个网标记红色因为最小和/或阻抗值在这些网外的34±5%左右(32.3到35.7欧姆)。约束管理器显示阻抗范围从32.069到46.62欧姆;这些值可以出现在这些地方网。这些可能是由于意想不到的寄生耦合与其他导体,跟踪宽度的变化,或路由在一个参考的空白飞机。

注意,快板约束管理器还允许您定义其他物理和电气约束你的PCB。物理约束管理方面像垫和跟踪间距,而电气约束传播延迟的限制和管理方面返回路径跟踪。

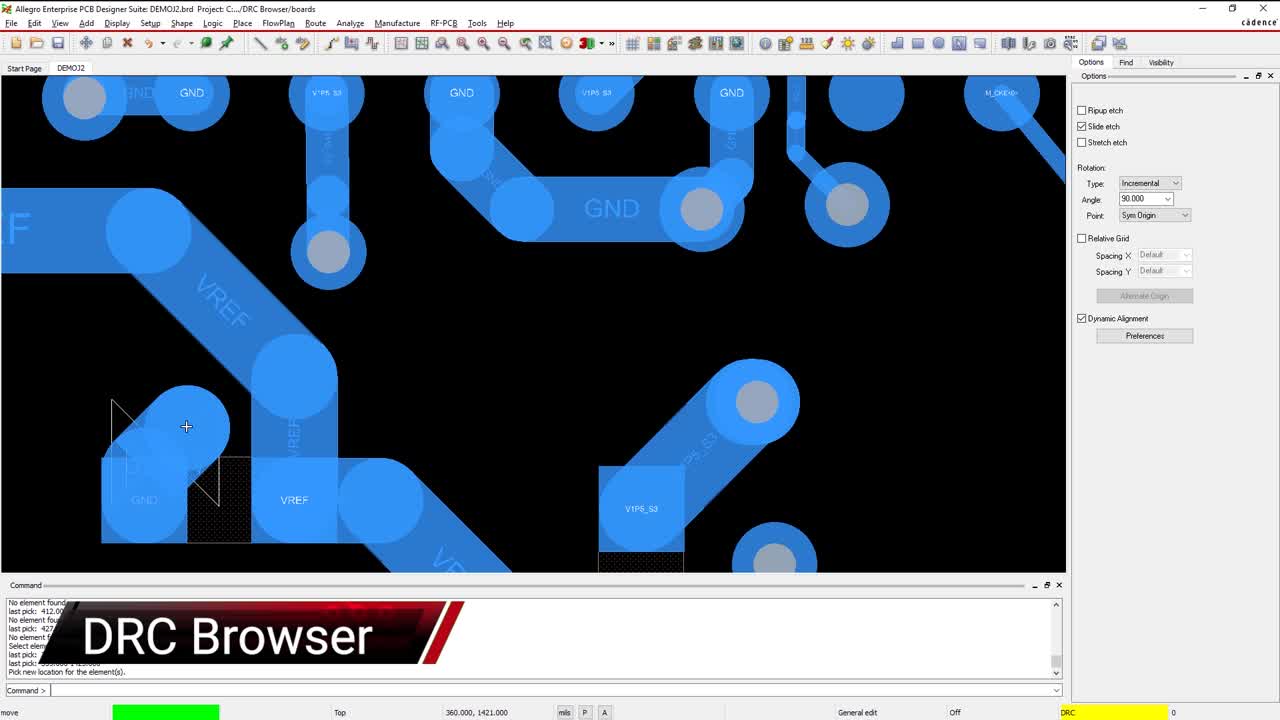

一旦发现违反设计规则网,你可以得到更详细的哪些部分设计违反你的设计约束。视图约束违反的另一种方法是使用刚果民主共和国浏览器从工具菜单中。这将显示你在董事会违反坐标设计约束,将在不同的类别标记特定约束违反。阅读这个列表的违反可以麻烦,但快速的提供了可视化的工具约束违反。这涉及到一些从你的布局布线后仿真数据。

阻抗和反射模拟运行

一旦你准备好正确的点阻抗不匹配你的板,您可以使用在急速地发现信号完整性分析特性阻抗的变化与反射和确定位置。要做到这一点,打开你的董事会在快板,单击分析菜单,选择工作流管理器选项。这将弹出几个分析可以执行,包括反射阻抗工作流和工作流。

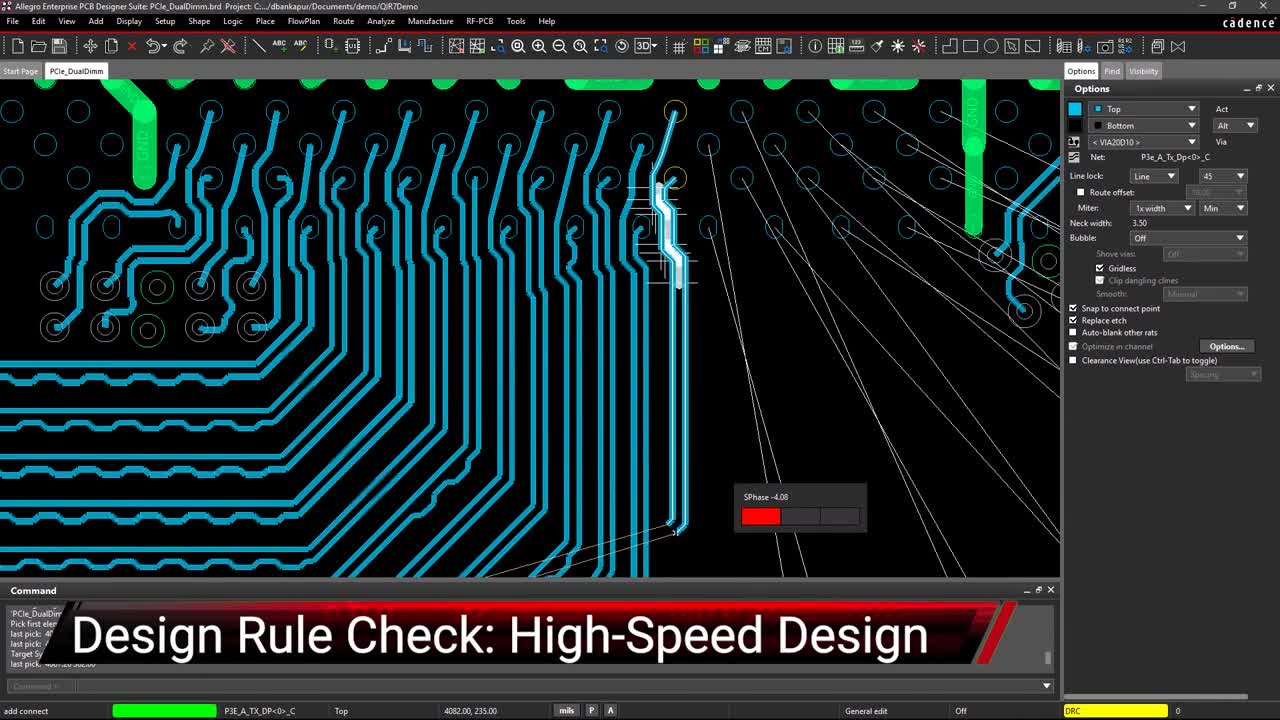

开始,选择反映工作流和篮网要检查。选择篮网之后,单击“开始”开始仿真分析。模拟器完成后,您可以单击反映视觉看到热图国旗的位置反射在你选定的网。您还可以点击反射表查看特定过度/脱靶量和他们在董事会的坐标。因为我们正在处理DDR行黑板上,可以比较的值对反射电平规格表。

下图显示了四个集团网一些反射的结果我们已经检查。从这张图片,我们看到反射主要发生在组件垫。这些值以红色标记,只有生产~ 10 mV的回弹。30 mV回弹稍早在互联和不易可视化反映视觉工具;你需要双击相应的输入阻抗表中看到这些结果。

反映工作流的结果。

沿着这些网30 mV回弹发生在多个点附近的长度匹配段早期图像所示。阻抗的工作流分析可以帮助你解释这些反射引起的阻抗变化沿互连,当看到视觉将会变得更明显。

检查阻抗变化,分析工具栏选择阻抗工作流选项。选择相同的网分析和仿真运行。整个互连阻抗可以通过选择阻抗视觉选项,这将再次显示热点图与彩色阻抗值。

四网阻抗变化。

从这里,我们可以立即看到阻抗使突然从~ 46 ~ 34欧姆欧姆,正如在急速地约束经理表示。这应该是显而易见的从红之间的长度变化部分和蓝色部分。这对应于该地区在这些网高过头。这里,下一步是比较你的信号过度和阻抗变化对信号标准。红色的部分这些网的一部分从BGA扇出在一个FPGA,所以你会有多宽有限你可以展开部分,防止过度的反射和损失。

上面所示的相同的仿真步骤可以用来检查不同的双网你的董事会。您只需要选择两端的双微分阻抗保持一致,确保整个董事会。与微分对,你还需要检查符合长度匹配的公差,可以定义在急速地约束管理器。刚果民主共和国浏览器可以用于确定长度匹配的违规行为发生,和路由工具会让你适用标准长度匹配段保持微分对同步。

如果你想了解更多关于节奏是如何对你的解决方案,跟我们和我们的专家团队。