匹配的终止有助于避免阻抗问题

直到19世纪中期,个人交流——无论多么重要——都需要几天甚至几个月的时间。但是……创新——尽管被贴上了“不切实际或疯狂”的标签——坚持了下来。

在电报发明之前,把电与一种可以远距离发送信息的设备结合起来的可能性似乎是非常荒谬的。即使在那时,发送信息也需要有人驻扎在发报局,另一个人驻扎在收报局,弯腰在一个完成电路的电报键前。很多时候,多个发送和接收办公室以及多个操作员帮助通过两条电线传输消息。

质量差的信号线和作为电源的低效电池阻碍了电流。隐私不是问题,因为没有消息是私密的。利用……轻……嗒……丝锥。每个接收站都需要能把摩尔斯电码翻译成可理解信息的操作员。电流提供了移动指示器指针和蜂鸣器所需的电力,使操作员能够听到消息。

我们用最新的技术完成同样的任务,但方式更顺畅、更私密、更快捷。但是,仍然存在一些同样的限制因素。携带电信号的导线的特性决定了信号在导线中传播时的有限速度。将高速信号连接到长传输线上可能会引入与信号上升时间相等的延迟。每条传输线都有电阻、电感和电容。而且,每条传输线仍然容易受到反射和振铃的影响。

你需要时间来反思

当我们使用高速数字电路时,会出现传播延迟。从电路的角度来看,延迟似乎可以模仿信号转换时间。我们不应该把线看作零延迟的完美导体,而应该把线看作传输线。当从传输线的角度观察导体时,信号变化发生在输出改变状态之后。

将两个导体平行放置在PCB上可以创建一个简单的传输线。如果我们有无限长的迹线,并立即在迹线对上放置电压源,电流就会产生一个沿迹线对愉快传播的电压波。不幸的是,无限长的PCB走线只在理论上存在,而在实践中并不存在。

相反,我们的痕迹-作为传输线-长度是有限的。在电极对上施加电压会产生电流。Kirchoff告诉我们,如果我们用特征阻抗以外的任何值终止迹线,电压波将沿线向下传播并与原始电压波相遇。虽然这次会面可能会让你瞬间成为朋友,但事情也可能会出错。具有相反极性的反射电压波将抵消原始电压波。相反,具有相同极性的反射电压波将增加原始波。

反射系数(ρ)决定了反射波的振幅。该系数的值等于线路末端的终止阻抗(Zterm)减去特征阻抗(Z0)除以终止阻抗加上特征阻抗。在方程形式中,反射系数为:

ρ = Zterm - Z0 / Zterm + Z0

当传输线的阻抗沿其长度变化时,反射就会发生。各种各样的因素,比如存根,过孔,连接器,组件包,以及不匹配的驱动器和负载-可以改变阻抗。当信号来回反射时,负载上会发生另一种叫做振铃的现象。振铃固有的振荡会导致假触发和噪声,同时减少接收机的范围。

在设计中确保适当的信号完整性可能是一个巨大的痛苦,如果不始终检查。

当源的阻抗等于迹线的阻抗和负载的阻抗时,存在迹线的最佳能量传递。使用一个等于传输线的特性阻抗终止这条线可以避免反射。通过用特性阻抗终止迹线,我们匹配传输线的两端。终端电阻使阻抗相等。

耳鸣困扰着我

在PCB设计中,可以通过保持迹线电性短(不超过信号边缘上升时间的三分之一)来停止反射和振铃。使用这种方法,原始信号的上升或下降沿会包围并淹没任何反射信号。

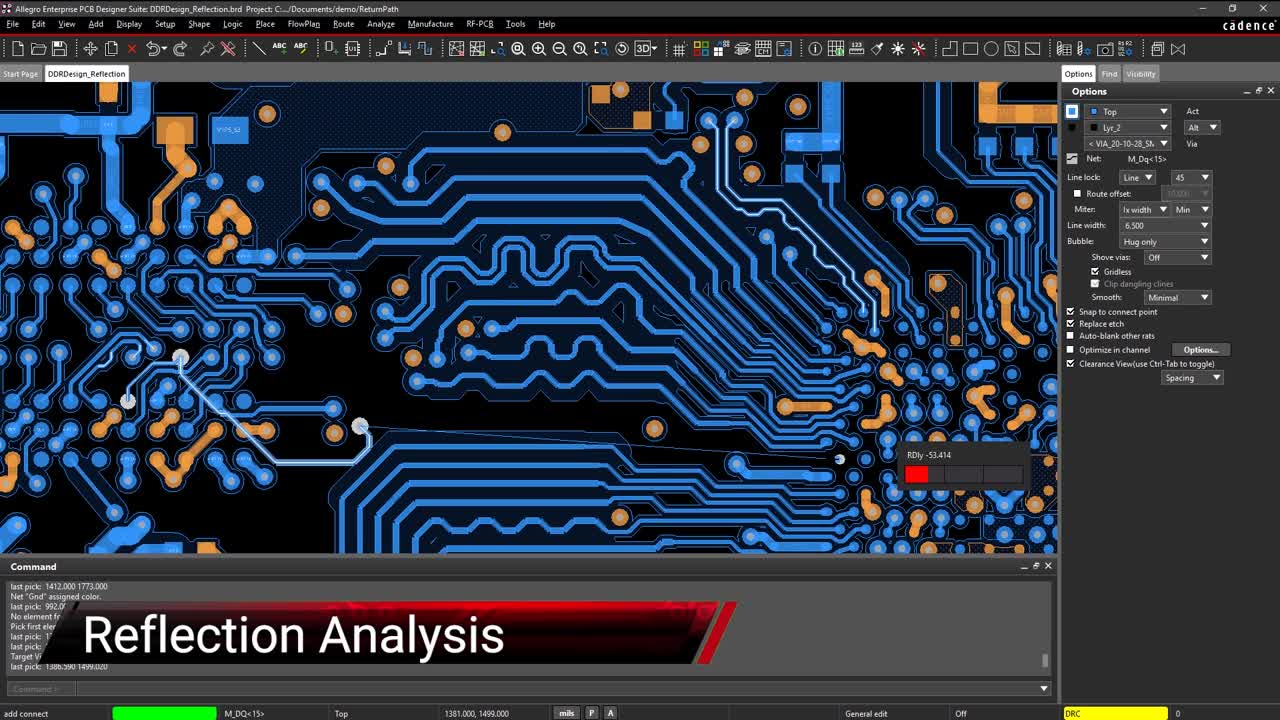

如果PCB设计不能实现电气短走线,则可以使用PCB设计软件中的模拟来查找匹配走线和负载所需的源阻抗量。您的设计软件提供了选择连接源或负载附近的终端电阻值的工具,以及指定用于匹配阻抗的方法的设计规则。所选择的终止方法取决于元件占地面积、跟踪路由和电路的有效工作频率。有效工作频率为:

信号频率(GHz) = 0.35 /信号转换时间(nSec)

试试这些神奇的方法!

阻抗匹配消除了由信号退化、反射和线路噪声引起的数据错误。考虑到这一点,让我们再看一下跟踪终止的需求。用于实现匹配终止的常用方法包括串联、并联、Thevenin和AC终止。以时钟驱动程序为例,串联终止在驱动程序的输出端增加一个终止电阻。增加电阻匹配源阻抗和跟踪阻抗,同时增加线源阻抗。

应用系列终止可以完成几件事。通过降低线路噪声和电磁干扰,驱动器边缘率降低,信号质量提高。但是,由于串联终止不会终止负载,因此串联终止的迹线只会抑制振铃,而不会停止反射。使用串联终止也减慢了信号的上升和下降时间。由于这最后一个因素,串联终止适用于单一和双传输,但不适用于分布式负载。

同样以时钟驱动程序为例,并行终端在负载处放置一个电阻,而不是在跟踪的源端。用这种方法,终端电阻器的值与负载阻抗和线路阻抗的值相匹配。将电阻器放置在负载端可以通过吸收和耗散能量来防止反射。

与平行终止一样,戴维南终止防止从负载端反射信号。Thevenin方法在负载端放置并联组合的电阻,以匹配负载和跟踪阻抗。这种配置平衡了集成电路的高、低逻辑电平。

用于电缆、背板和分布式负载,最后一种匹配的终止方法(称为交流终止)使用高通滤波器终止负载端。交流终止方法依赖于一个RC时间常数,它仍然大于信号的往返传播时间。由于电容可以屏蔽低频噪声,从而降低了静态功耗。

Cadence不仅如此这套设计和分析工具建立与您和您的团队的需求,但也有布局能力,使任何信号和阻抗困难容易。Allegro PCB Designer配备了先进的DRC引擎,能够规划任何阻抗挑战,以及增强信号完整性分析和无缝过渡到布局后的信号分析。

如果您想了解更多Cadence如何为您提供解决方案,跟我们和我们的专家团队谈谈吧.