信号完整性基础的PCB布局

关键的外卖

探索信号完整性基础

PCB布局好的信号完整性的技术

布局工具和特性,可以帮助提高信号的完整性

完整性的定义特点之一是一致的和不妥协的行为可以被信任。这就是为什么完整性也用来定义高速电信号的质量在现代电子设备和系统。我们相信这些信号来做这项工作,他们做设计的。然而,信号退化,或者可怜的信号完整性,不能完成他们的目的。这可能导致各种各样的问题在电子设计,从间歇性中断彻底失败。

为了防止这些混乱和失败,印刷电路板需要被放置根据特定的路由设计标准促进高速信号传输的最佳环境。这涉及到PCB设计的方方面面,包括部分使用,原始的电路板的制作,以及部分排列和连接在一起。成功地设计高速电子产品,它是必不可少的设计师理解信号完整性的基本面。

潜在的问题由于糟糕的信号完整性

干扰的影响电子设备的操作可以很戏剧性。多年来,空乘人员敦促我们关闭我们的手机或对无线电产生静电而不是清晰的音频。甚至一些老电脑辐射EMI,他们最终退出市场。然而,大多数问题引起的信号完整性差通常比这更微妙的可能是偶尔的性能故障,数据可能会下降,或设备甚至可能无法在极端情况下运作。所有这些问题通常可以追溯到信号完整性问题。

由于信号速度的增加在我们的电子产品,他们更容易受到各种积极的干扰。这些可以包括由于反射信号阻抗不匹配、地面反射和串扰。如果电路板没有明确提出了应对这些问题、信号退化可能还会继续,直到它不再是设计。此外,电路板必须设计,这样它不会创建自己的电路信号完整性问题或附近的电子产品。在我们看看如何设计这些问题,让我们先看一些关键信号完整性的基本面。

信号完整性的基本面需要注意的

信号完整性基本面电路板这样的成功的关键

电路板上的信号可以有它质量退化由于许多不同的效果,而这些可以分为不同的群体。这里有四个主要领域的信号完整性差,你应该知道的。

电磁干扰(EMI)

高频信号辐射EMI如果不注意他们是如何路由在电路板上。痕迹的长度和配置不仅可以是一个问题,但通过存根可以作为一个跟踪和天线。EMI的另一个来源是信号返回路径,它应该在一个最优相邻参考面。如果返回路径被以任何方式,信号将辐射更多的噪声,因为它寻求一条回到源头。

无意的电磁耦合(相声)

高速痕迹太近可能无意中压倒其他夫妇有一个信号。这串扰可以导致受害者信号模拟侵略者的特征信号,而不是它的目的是执行任务。这不仅是并排的痕迹的问题,还有痕迹,并行路由的相邻层板上。这种类型的相声是称为侧向耦合和为什么大多数电路板设计替代水平和垂直路由方向上相邻层。

同步开关噪声(地面反弹)

组件的数量高低状态之间的切换在电路板上,电压水平可能不会返回到地面的潜力应该开关时低。如果低的电压电平状态反弹太高,低的信号可能会错误地解释为高状态。当很多同时发生这种情况,它可能会导致错误或双交换和干扰电路的操作。

阻抗失配

变化敏感的一致性高输电线路会导致信号反射,扭曲了信号的完整性。跟踪路由没有适当的注意他们的阻抗值会改变这些值在不同地区根据不同的条件。正确路径阻抗控制敏感痕迹需要特定的层配置,跟踪宽度和间隙。

定义了信号完整性的主要问题后,现在让我们看看一些PCB设计技术,可以弥补这些问题。

PCB层配置和组件的位置

印刷电路板的信号完整性问题往往是由于不当的信号返回路径。返回路径不仅需要自由的障碍,但它需要一个相邻参考平面层最好的信号完整性。这个配置需要安排板层分层盘旋飞行与高速专用层敏感路由和相邻参考平面微带或带状线配置。微带配置由表面痕迹与单个平面下方,而带状线内部跟踪路由和夹在两个参考平面。

微带和带状线层配置因素到信号的完整性

虽然所有信号将受益于拥有一个相邻参考面为一个明确的返回路径,它变得更加重要的敏感信号,必须击败阻抗控制。计算介质宽度和持续跟踪厚度将决定跟踪宽度控制阻抗路由。因为改变董事会层分层盘旋飞行或用于PCB制造的材料会改变这些计算,设计师必须确定董事会布局配置布局开始之前。这些计算也将取决于是否impedance-controlled跟踪路由使用的微带之一或带状线配置,如上所示。

与板层分层盘旋飞行配置确定,下一步是将组件在黑板上。许多高速电路由多个网,从源或司机销一个组件,持续到其他地方,然后终止负载销的最终的组件。这些电路被称为信号路径。保持信号完整性,他们必须有部分放置在序列,详细的示意图,以允许针之间的最短的点对点连接。其他组件,如处理器和内存芯片,需要间隔得足够远以允许所有的路由拓扑,但足够近短连接。以下是一些要点组件的位置要记住:

- 遵循的逻辑流程示意图在放置高速电路。

- 旁路电容接近每个权力销的处理器和内存设备。

- 允许逃跑的余地路由和路由。

- 坚持你的汇编可制造性设计(DFM)规则。

- 确保hot-running组件的热耗散。

在董事会的部分,下一步是路由。

电路板跟踪路由和参考平面

微分对电路板的路由

在这一点上,你将准备好开始跟踪路由,但是,记住,对信号完整性好,跟踪路由组件是如何定位密切相关。逃避路由,例如,必须精心设计,以确保所有相关的信号连接,组件,像绕过限制,尽可能接近别针。许多设计依赖via-in-pad大型引线数小袋保持连接短和开放更多的路由。

与部分放置在最优位置,你将在最好的位置路由高速电路成功。首先,然而,有一些指导方针要记住当你:

- 保持信号路径短,直接痕迹。

- 敏感的信号应该是路由之间的内部层和旁边或参考飞机尽可能。

- 时钟线和其他敏感应单独进行高速信号从其他尽可能多的痕迹。一个好的经验法则是间距应该跟踪的三倍宽。

- 保持微分对路由紧密在一起,不像一对在障碍通过分裂。

- 当路由组的网中所有匹配长度,最长的开始连接第一和添加优化转向其他人为了匹配第一个。

- 路线不敏感的信号通过电路的噪声区域,如模拟或董事会的电源部分。

- 给自己足够的空间为特定路由拓扑,如菊花链,如果必要的。

- 尽可能减少使用通过避免他们的长度和电感,可以引入更多的信号完整性问题。

除了路由,您还需要设计董事会的权力交付网络(生产)。开发一个清洁生产是必要的对权力的完整性,也是良好的信号完整性的一部分。也是很重要的一个方面,你并不路线高速通过地区输电线路阻塞的参考平面。这可以增加EMI董事会产生的信号徘徊试图找到一个明确的返回路径源。堵塞可以包括分裂飞机、董事会图样或通过致密区域,如下图所示。

致密区域通过可以创建一个阻塞的信号返回路径参考平面上

设计一个电路板保持良好的信号完整性是一个大量的工作。幸运的是,有一些优秀的CAD工具可以帮助功能。

布局可以帮助设计师保持信号完整性的工具

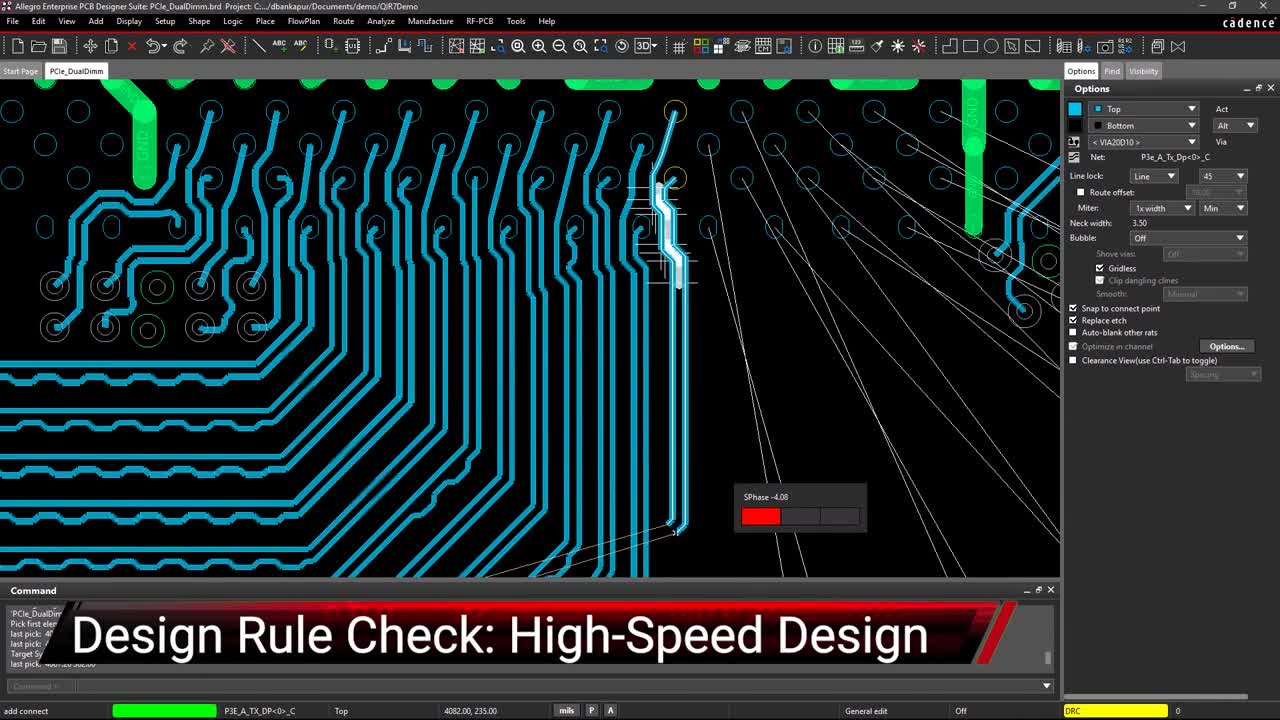

今天的PCB设计系统包含许多有用的工具和功能,这将帮助你保持良好的信号完整性设计。例如,快板PCB编辑器从节奏约束系统,允许你设置规则组件,网,高速网,甚至电阻抗和传播延迟等属性。此外,Sigrity极光工具提供了在设计分析能力允许无缝集成的信号完整性、力量,和电磁模拟直接进入您的布局环境。节奏也为电路仿真提供了一套工具,auto-routing和信号分析。

更多信息高速设计和信号完整性的基本面,看看这个电子书。

如果你想了解更多关于节奏是如何对你的解决方案,跟我们和我们的专家团队。